- May -akda Lynn Donovan donovan@answers-technology.com.

- Public 2023-12-15 23:54.

- Huling binago 2025-01-22 17:43.

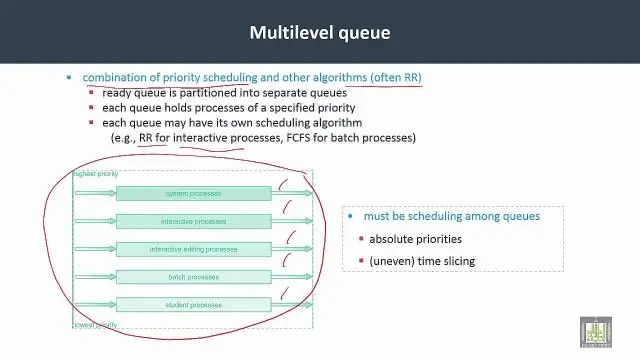

Multilevel Queue Scheduling . A marami -level pag-iskedyul ng pila algorithm partitions ang handa pila sa ilang magkakahiwalay mga pila . Ang mga proseso ay permanenteng nakatalaga sa isa pila , sa pangkalahatan ay nakabatay sa ilang katangian ng proseso, gaya ng laki ng memorya, priyoridad ng proseso, o uri ng proseso.

Katulad nito, ano ang multi queue?

Marami - pila hinahayaan kang mag-configure ng higit sa isang trapiko pila para sa bawat suportadong interface ng network, upang higit sa isang SND CPU ang makayanan ang trapiko ng isang interface ng network sa isang pagkakataon. Mahusay nitong binabalanse ang load sa pagitan ng mga SND CPU at CoreXL firewall instance CPU.

Alamin din, ano ang multilevel feedback queue scheduling? Multilevel Feedback Queue Scheduling . Sa isang multilevel na pila - pag-iiskedyul algorithm, ang mga proseso ay permanenteng itinalaga sa a pila sa pagpasok sa system. Pag-iiskedyul ng pila ng feedback sa maraming antas , gayunpaman, ay nagbibigay-daan sa isang proseso na lumipat sa pagitan mga pila . Ang ideya ay upang paghiwalayin ang mga proseso na may iba't ibang katangian ng CPU-burst.

Maaaring magtanong din, ano ang 3 magkakaibang uri ng mga pila sa pag-iiskedyul?

Tatlong uri ng scheduler ay 1) Pangmatagalan 2) Maikling termino 3 ) Katamtamang termino. Pangmatagalan scheduler kinokontrol ang programa at piliin ang proseso mula sa pila at ini-load ang mga ito sa memorya para sa pagpapatupad. Ang medium-term scheduler nagbibigay-daan sa iyo na pangasiwaan ang mga pinagpalit na proseso sa labas.

Ano ang pagkakaiba sa pagitan ng multilevel queue at multilevel feedback queue?

2. Sa Multilevel na pila (MLQ) ang mga proseso ay permanenteng nakatalaga sa isa pila batay sa kanilang laki ng memorya, priyoridad ng proseso o uri ng proseso. Sa Multilevel Feedback queue (MLFQ) pinapayagan nito ang isang proseso na lumipat sa pagitan ang mga pila , ayon sa mga katangian ng kanilang pagsabog ng CPU.

Inirerekumendang:

Ano ang maximum visibility timeout ng isang SQS message sa isang queue?

Upang pigilan ang ibang mga consumer na iproseso muli ang mensahe, nagtatakda ang Amazon SQS ng visibility timeout, isang yugto ng panahon kung saan pinipigilan ng Amazon SQS ang ibang mga consumer na matanggap at maproseso ang mensahe. Ang default na timeout ng visibility para sa isang mensahe ay 30 segundo. Ang pinakamababa ay 0 segundo. Ang maximum ay 12 oras

Ano ang queue sa istruktura ng data gamit ang C?

C program para ipatupad ang queue gamit ang array/linear na pagpapatupad ng queue. Ang QUEUE ay isang simpleng istraktura ng data, na mayroong FIFO (First In First Out) na property kung saan ang Mga Item ay inaalis sa parehong pagkakasunud-sunod ng paglalagay ng mga ito. Ang QUEUE ay may dalawang pointer na FRONT at REAR, ang Item ay maaaring itulak ng REAR End at maaaring alisin ng FRONT End

Maaari ba nating ipatupad ang stack at queue gamit ang naka-link na listahan?

Ang bawat node ay may halaga at isang link sa susunod na node. Dalawang sikat na application ng naka-link na listahan ay stack at queue. Queue: Ang Queue ay isang istraktura ng data, na gumagamit ng First in First out (FIFO) na prinsipyo. Maaaring ipatupad ang queue sa pamamagitan ng stack, array at linked list

Ano ang Cron Job Scheduling?

Ang Cron ay isang daemon sa pag-iiskedyul na nagsasagawa ng mga gawain sa mga tinukoy na agwat. Ang mga gawaing ito ay tinatawag na mga cron job at kadalasang ginagamit upang i-automate ang pagpapanatili o pangangasiwa ng system. Ang mga cron job ay maaaring iiskedyul na tumakbo ng isang minuto, oras, araw ng buwan, buwan, araw ng linggo, o anumang kumbinasyon ng mga ito

Paano ko gagamitin ang SQS queue?

Pagsisimula sa Amazon SQS Hakbang 1: Gumawa ng Queue. Ang una at pinakakaraniwang gawain ng Amazon SQS ay ang paglikha ng mga pila. Hakbang 2: Magpadala ng Mensahe. Pagkatapos mong gawin ang iyong queue, maaari kang magpadala ng mensahe dito. Hakbang 3: Tanggapin at Tanggalin ang Iyong Mensahe. Pagkatapos mong magpadala ng mensahe sa isang queue, maaari mo itong ubusin (bawiin ito mula sa pila). Hakbang 4: Tanggalin ang Iyong Queue